IEEE 1838-2019 pdf download.IEEE Standard for Test Access Architecture for Three-Dimensional Stacked Integrated Circuits

Like all micro-electronic products, these die stacks need to be tested before they can be shipped with acceptable quality levels to their customers. We distinguish the following tests: (1) pre-bond tests prior to stacking, (2) mid-bond tests on incomplete, partial stacks, (3) post-bond tests on complete yet not packaged stacks, and (4) fnal tests on the fnal packaged product. The number of possible test fows grows quickly with the number of dies in the stack and hence is subject of automated trade-off evaluation and optimization (see, [B1], [B4], and [B8]).

1.3 Motivation for a 3D-DfT standard A well-architected DfT access infrastructure is indispensable for achieving a high-quality test. Not only do we need conventional 2D-DfT structures (such as internal scan chains, test data compression circuitry, IEEE Std 1500 wrappers around embedded cores, and/or built-in self-test (BIST) engines) that provide test access within a single die, we also need new approaches for testing stacked systems. Especially once a (partial or complete) vertical stack has been formed (i.e., in mid-bond, post-bond, or fnal testing phases), we also need novel 3D-DfT structures that provide test access from (and to) the external stack I/Os to (and from) the various dies and inter-die interconnects. For example: if a stack consists of three dies and test access from external test equipment is exclusively possible via the stack I/Os that are concentrated in, say, Die 1, then Die 1 and Die 2 need to cooperate in transporting test stimuli and responses up and down the stack in order to be able to test Die 3.

To enable separation of the test development as well as test execution for the various dies in the stack, the 3D-DfT architecture should enable modular testing, i.e., tests for dies and interconnect layers between adjacent stacked dies can be developed and executed individually. Several ad-hoc 3D-DfT architectures have been proposed, among others based on IEEE Std 1149.1, IEEE Std 1500, and IEEE Std 1687. These architectures all have their specifc strong and weak points. However, these ad-hoc 3D-DfT architectures do not inter-operate together. Hence, there is a need for a per-die 3D-DfT standard, such that if compliant dies (even if designed and developed by different teams or different companies) are brought together in a die stack, a basic minimum of test features should work across the stack. This is exactly the aim of IEEE Std 1838.

1.4 Context The Standard for Test Access Architecture for Three-Dimensional Stacked ICs is conceptually related to previously developed design-for-test (DfT) standards, in particular IEEE Std 1149.1, IEEE Std 1500, and IEEE Std 1687. The frst two standards specify test access architectures for ICs on boards (IEEE Std 1149.1) and IP cores embedded within an IC (IEEE Std 1500). IEEE Std 1687 describes an access architecture to embedded instruments. These three previously developed standards have infuenced and are referred to in this standard, so a solid understanding of these standards is strongly recommended.

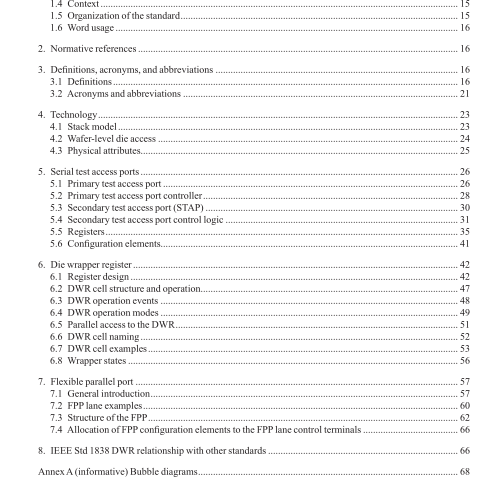

1.5 Organization of the standard

Clause 1 provides an overview and context for this standard.

Clause 2 provides references necessary to understand this standard.

Clause 3 defnes terminology and acronyms used in this standard.

Clause 4 is a tutorial that outlines the technologies addressed and utilized by this standard.

Clause 5 defnes the serial access bus and structure which forms the mandatory basis of the standard.

Clause 6 specifes the construction of the mandatory die wrapper register.

1.6 Word usage

The word shall indicates mandatory requirements strictly to be followed in order to conform to the standard and from which no deviation is permitted (shall equals is required to). 3,4

The word should indicates that among several possibilities one is recommended as particularly suitable, without mentioning or excluding others; or that a certain course of action is preferred but not necessarily required (should equals is recommended that).

The word may is used to indicate a course of action permissible within the limits of the standard (may equals is permitted to).

The word can is used for statements of possibility and capability, whether material, physical, or causal (can equals is able to).IEEE 1838 pdf download.IEEE 1838-2019 pdf download

IEEE 1838-2019 pdf download

Leave a Reply